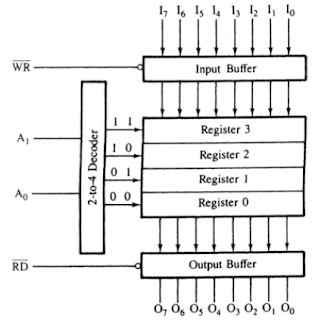

أربع سجلات موضوعة على التوالي طول كل منها 8 بت. نحتاج عند الكتابة أوالقراءة من أحد هذه السجلات إلى اختيار أو تأهيل ذلك السجل. يمكننا تأهيل أحدالسجلات باستخدام

مفكك ترميز decoder 2 إلى 4 2- to 4)) .

نحتاج في هذه الحالة إلى مدخلين إضافيين A0 و A1 يؤخذان من خطوط عنونةaddress lines المعالج.

تشكل قيمة A0 و A1 أربع ثنائيات مختلفة: 00 , 10 ،01 و 11 تُحدد أو تعنون كلتشكيلة أحد السجلات: register 0 إلى .register 3جرى الاستعاضة، في الشكل، عنEN بالخطين A0 و .A1

عند زيادة عدد السجلات في الشكل السابق إلى 8 فإننا نصبح بحاجة إلى 3 خطوطعنونة لعنونة أي سجل أو موقع في الذاكرة. وعلى نحو عام يلزمنا log2 L خط عنونة فيحالة ذاكرة تضم L سجلاً.

اختبار ذاتي: ما هو عدد خطوط العنونة اللازمة لعنونة ذاكرة بحجم 1024 بايت؟

الحل: .log21024 =10

تبين الصورة التالية مثالا نمطيًا عن ذاكرة للقراءة والكتابة )تسمى أيضًا الذاكرة الحية(وعلى

المغارز التي تتضمنها. تضم مغارز الذاكرة 62256 ، التي يبلغ حجمها 8 32 K ×بت،خطوط العنونة والمعطيات وإشارات التحكم التالية:

- خطوط الذاكرة: تضم الذاكرة 15 62256 خط عنونة .(A0-A14) 62256 ويجري وصلهذه الخطوط إلى خطوط عنونة المعالج، عند وضع الذاكرة في نظام مبني حول معالج.

خطوط المعطيات: تضم الذاكرة 62256 ثماني خطوط معطيات (D0-D7 ) , وبالتالييمكننا تخزين بايت واحد في أي موقع من الذاكرة. ُتوصل خطوط المعطيات إلى خطوطمعطيات المعالج

أضف تعليق:

0 comments: