في التدوينات الماضية بعض تاريخ عائلات المعالجات CPU – computer interface ثم تحدثنا عن معالجات 4CISC و معالجات RISC وذكرنا الفرق بين معالجات 4CISC و معالجات RISC ومبدأ المعالجة التواردية

واليوم نتعرف بشكل مفصل عن السجلات الداخلية للمعالج 8088/ 8086

رتل التعليمات instruction queue :

يسمح رتل التعليمات بزيادة سرعة تنفيذ البرامج، فبينما تكون وحدة التنفيذ مشغولة في معالجة المعطيات تعمل BIU على جلب تعليمات جديدة من الذاكرة. توضع هذه التعليمات ضمن مصفوفة من ذاكرة RAM داخلية، تُسمى رتل دفق التعليمات. يمكن لهذا الرتل تخزين أربع بايتات من التعليمات على الأكثر في المعالج 8088 وخزن 6 بايتات في المعالج 8086

على الأكثر.

تُنفذ الـ EU التعليمات التي تقرؤها من الرتل، الذي يعمل بطريقة "الداخل أولاً يخرج أولاً FIFO عندما تكون التعليمات التي تبحث عنها EUغير موجودة مسبقًا في الرتل فإنها تنتظر حتى تعمل BIU على جلبها من الذاكرة ووضعها في الرتل. يمكن أن يحدث ذلك مثلاً :

- عندما تحتاج التعليمة الحالية إلى معطيات من الذاكرة غير موجودة ضمن الرتل.

- عند تنفيذ تعليمة قفز أو استدعاءJUMP/CALL ، إذ يجري -عند تنفيذ هذه التعليمات- إفراغ محتوى الرتل وشحنه من جديد بالتعليمات ابتداء من الموقع الذي قفزت إليه التعليمة.

سجلات المقتطعات Segment Registers

يستطيع المعالج 8086/8088 عنونة ذاكرة تصل سعتها حتى 1 ميغابايت. وتحتل هذه الذاكرة العناوين الحقيقة أو الفيزيائية من 00000 h حتى FFFFFh .

نحتاج لعنونة ذاكرة بحجم 1 ميغابايت إلى 20 خط عنونة، ول ما كان طول السجلات الداخلية للمعالج 8086/8088 هو 16 بتًا، فقد قسمت ذاكرة المعالج 8086/8088 إلى مقتطعات منطقية logical segments طول كل منها 64 كيلوبايت. تحتوي وحدة التواجه أربعة سجلات مقتطعات DS ،SS ،CS و ES طول كل منها 16 بت، ويُؤشر كل سجل على بداية مقتطع محدد من الذاكرة .

وللحصول على العنوان الفيزيائي ممثلا على 20 بت، تقوم وحدة التواجه بإزاحة محتوى سجل المقتطع المُستخدم أربع بتات نحو اليسار (فتصبح قيمة العنوان مُمثلة على 20 بت) ثم يُضاف إليها قيمة انزياح ممثلة على 16 بت. وبذلك، يمكن للمقتطعات أن تبدأ من أي موقع في الذاكرة شريطة أن ينتهي عنوان هذا الموقع بأربعة أصفار. تسمح بعض تعليمات المعالج بقراءة هذه السجلات وتغيير محتواها، مما يُمكننا من عنونة كامل فضاء ذاكرة المعالج.

تحتوي وحدة التواجه على جامع adder يُستخدم خصيصًا لتشكيل العنوان الفيزيائي بطول 20 بت.

CS سجل مقتطع البرنامج Code Segment

يُؤشر هذا السجل إلى بداية مقتطع التعليمات، ويجب أن تقع جميع تعليمات البرنامج ضمن هذا المقتطع.

SS سجل مقتطع المكدس Stack Segment

يُؤشر هذا السجل إلى بداية مقتطع المكدس الحالي .

DS سجل مقتطع المعطيات Data Segment

يُؤشر هذا السجل إلى بداية مقتطع المعطيات الحالي، تقع معظم المعطيات التي يحتاجها البرنامج أثناء تنفيذه للتعليمات ضمن هذا المقتطع.

ES سجل المقتطع الإضافي Extra Segment

يُؤشر هذا السجل إلى بداية مقتطع المعطيات الإضافي.

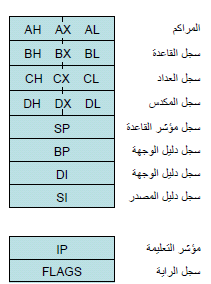

سجل مؤشر التعليمة IP

يجري حساب العنوان الفيزيائي للتعليمة باستخدام السجل IP وسجل مقتطع البرنامج CS .

يجري آليًا زيادة قيمة السجل IP بواحد أو أكثر بعد قراءة كل تعليمة من الذاكرة وذلك من أجل عنونة التعليمة التي ستجلب تاليًا.

دارات توليد إشارات تحكم المسرى(Bus)

تولد هذه الدارات إشارات التحكم بالمسرى مثل إشارات القراءة والكتابة من/في الذاكرة والبوابات.

وحدة التنفيذ

تحلل وحدة التنفيذ التعليمات التي قامت BIU بجلبها مسبقًا وتنفذها، وهي تحتوي على الأجزاء الرئيسة التالية:

دارات تفكيك كود التعليمة:

ُتترجم هذه الدارات التعليمة بعد قراءتها من الرتل إلى سلسلة أفعال يجري تنفيذها لاحقًا من قبل وحدة الحساب والمنطق.

وحدة الحساب والمنطق ALU :

تنفذ هذه الوحدة التعليمات الحسابية الأساسية مثل الجمع والطرح والعمليات المنطقية البسيطة مثل AND و OR والازاحة .

سجلات عامة general registers :

تحتوي وحدة التنفيذ على 8 سجلات عامة طول كل منها 16 بت وهي ،CX ،BX ،AX SI ،BP ،SP ،DX و DI .

إن السجلات DX ،CX ،BX ،AX هي للاستخدام العام، وُتستخدم عادة للتخزين المؤقت للمعطيات أو للنتائج. يمكن استخدام هذه السجلات لتخزين معطيات ممثلة على 16 بت أو تقسيم كل منها إلى سجلين: أعلى وأدنى وخزن في كل منها معطيات بطول 8 بت على سبيل المثال، يمكن اعتبار السجل DX سجلين كل منها بثماني بتات هما DH (البايت الأعلى من DX) و DL (البايت الأدنى من DX).

أما السجلات DI و SI ،BP ،SP فطول كل منها 16 بت، ولا يمكن تقسيم أي منها إلى سجلين.

AX :

يقوم الـ AX بدور المراكم في العمليات التي تستخدم معامل معطيات بطول 16 بت، بينما يقوم AL بدور المراكم في العمليات على ثماني بتات فقط.

BX سجل القاعدة Base register

وهو سجل للاستخدام العام ويمكن أن يستخدم في عنونة الذاكرة.

CX سجل العداد Counter register

وسُميّ كذلك لأن بعض التعليمات مثل الإزاحة والحلقات تستخدمه كعداد.

DX سجل المعطيات Data Register

وتستخدم، ضمنيًا، في عمليات الجداء والقسمة، وفي العنونة غير المباشرة لبوابات الدخل/خرج.

SP سجل مؤشر المكدس Stack Pointer

يُستخدم في عمليات الوصول إلى المعطيات الموجودة في المكدس. يحتوي SP مقدار الانزياح عن بداية المقتطع الذي يشير إليه السجل SS .

تستخدم السجلات BP مؤشر القاعدة Base Pointer و SI دليل المصدر Source index و DI دليل الوجهه ، على نحو رئيس في تخزين قيمة انزياح موقع عن بداية أحد المقتطعات التي يُشير إليها أحد سجلات المقتطعات.

تُستخدم سجلات المعطيات في العمليات الحسابية والمنطقية المختلفة، كما تستخدم بعض

التعليمات ضمنيًا بعض السجلات العامة في تنجيزيها، كما هو مبين في الجدول:

سجل الراية أو الحالة Flag register

يحتوي سجل الراية في المعالج 8086/ 8088 على ستة رايات طول كل منها 1 بت هي ،AF PF ،SF ،OF ،CF و ،ZF تتغير حالة (قيمة) كل منها تبعًا لناتج تنفيذ بعض العمليات الحسابية أو المنطقية الحالية يُوفر المعالج تعليمات تسمح بتغيير تتابع تنفيذ التعليمات تبعًا لحالة هذه الرايات، مثل التعليمة JZ new ، والتي تعني اقفز إلى الموقع ذي الدالة new إذا كان ناتج العملية الحسابية أو المنطقية السابقة يساوي الصفر.

يحتوي سجل الراية أيضًا على ثلاث بتات تحكم وهي IF ،DF و TF تؤثر حالة هذه البتات في تنفيذ بعض التعليمات.

تُبين الصورة التالية أماكن توضع الرايات IF ،DF ،ZF ،PF ،SF ،OF ،CF ،AF و TF في سجل الراية :

AF راية الحامل المساعد Auxiliary Flag

يستخدم في التعليمات الحسابية العشرية المشفرة ثنائياً BCD ويساوي 1 في حال نَتج حامل بعد عملية جمع، أو استعارة بعد عملية طرح، وذلك بين نصف البايت (nibble) الأدنى ونصف البايت الأعلى.

CF راية الحامل Carry Flage

يساوي 1 في حالة وجود حامل بعد عملية جمع أو استعارة بعد عملية طرح، كما يمكن أن تتغير حالته أيضًا في عمليات الإزاحة.

OF راية الفائض Overflow Flag

يساوي 1 في حال تجاوز حجم ناتج العملية الحسابية سعة تخزين الوجهة .

SF راية الاشارة Sign Flag

يساوي 1 في حال كانت البت الأعلى من ناتج العملية يساوي 1 (أي كان الناتج سالبًا) .

PF راية الندبة Parity Flag

يساوي 1 في حال كان عدد الوحدان في ناتج العملية يساوي عددًا زوجيًا .

ZF راية الصفر Zero Flag

يساوي 1 في حال كان ناتج العملية الحسابية أو المنطقية يساوي الصفر.

DF راية الاتجاه Direction Flag

تسبب، عندما تساوي 1، إنقاصًا آليًا لمحتوى كل من السجلين DI و SI في تعليمات سلاسل المحارف أما حين تساوي 0 فتسبب زيادة آلية لهذا المحتوى .

IF راية المقاطعة Interrupt Flag

تسمح، عندما تساوي 1، بحدوث مقاطعة خارجية قابلة للحجب. أما عندما تساوي 0 فهي تحجب (تمنع) هذه المقاطعات.

TF راية التنفيذ الخطوي او المساري Trace Flag

تسمح، عندما تساوي 1، بإمكان تنفيذ البرنامج خطوة فخطوة .

نكتفي بهذا ونلتقي في التدوين القادم والذي سيكون تحت عنوان تنظيم ذاكرة المعالج 8086

عزيزنا الزائر إن كانت هذه اول زيارة لك لمدونتنا لا تنسى الاشتراك فيها عبر بريدك الالكتروني ليصلك كل جديد او قم بالإعجاب بصفحتنا على الفيس بوك في يسار الصفحة ....

أضف تعليق:

0 comments: